## 1000 MHz Quadrature Demodulator

#### **Description**

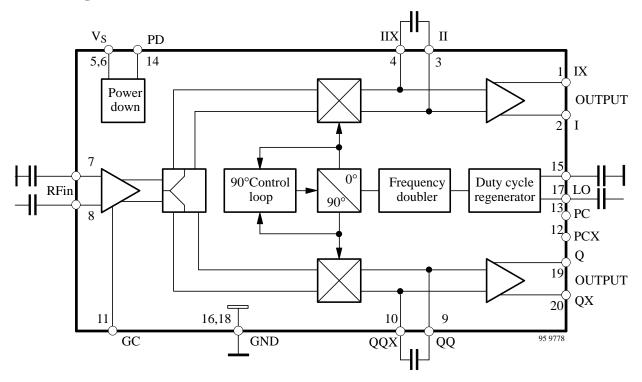

U2794B silicon monolithic integrated circuit is a quadrature demodulator that is manufactured using TELEFUNKEN's advanced UHF technology. This demodulator features a frequency range from 70 – 1000 MHz, low current consumption, selectable

gain, power down mode and is adjustment free. The IC is suitable for direct conversion and image rejection applications in digital radio systems up to 1 GHz such as cellular radio, cordless telephone, cable TV and satellite TV systems.

#### **Features**

- Supply voltage 5 V (typ.)

- Very low power consumption 125 mW (typ.)

- Very good image rejection by means of phase control loop for precise 90° phase shifting

- Duty cycle regeneration for single ended LO input signal

- Low LO input level –10 dBm (typ.)

- LO frequency from 70 MHz to 1 GHz

- Power down mode

- 25 dB gain control

- Very low I/Q output dc offset voltage typ. < 5 mV</li>

#### **Block Diagram**

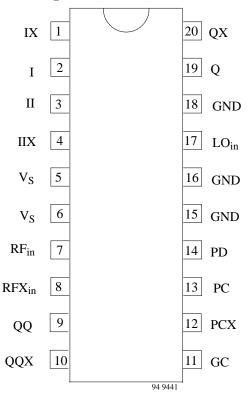

### **Pin Description**

| Pin | Symbol            | Function              |

|-----|-------------------|-----------------------|

| 1   | IX                | IX output             |

| 2   | I                 | I output              |

| 3   | II                | II low pass filter I  |

| 4   | IIX               | IIX low pass filter I |

| 5   | $V_{S}$           | Supply voltage        |

| 6   | $V_{S}$           | Supply voltage        |

| 7   | RFin              | RF input              |

| 8   | RFXin             | RFX input             |

| 9   | QQ                | QQ low pass filter Q  |

| 10  | QQX               | QQX low pass filter Q |

| 11  | GC                | GC gain control       |

| 12  | PCX               | PCX phase control     |

| 13  | PC                | PC phase control      |

| 14  | PD                | PD power down         |

| 15  | LOX <sub>in</sub> | LOX input             |

| 16  | GND               | Ground                |

| 17  | LO <sub>in</sub>  | LO input              |

| 18  | GND               | Ground                |

| 19  | Q                 | Q output              |

| 20  | QX                | QX output             |

#### Electrostatic sensitive device, observe precautions for handling!

### **Absolute Maximum Ratings**

|                           | Parameters       | Symbol         | Value        | Unit |

|---------------------------|------------------|----------------|--------------|------|

| Supply voltage            | Pins 5 and 6     | $V_{S}$        | 6            | V    |

| Input voltage             | Pins 7, 8 and 17 | V <sub>i</sub> | $0$ to $V_S$ | V    |

| Junction temperature      |                  | Tj             | 125          | °C   |

| Storage temperature range |                  | $T_{\rm stg}$  | -40 to 125   | °C   |

### **Operating Range**

| Parameters                        | Symbol           | Value        | Unit |

|-----------------------------------|------------------|--------------|------|

| Supply voltage range Pins 5 and 6 | $V_{S}$          | 4.75 to 5.25 | V    |

| Ambient temperature range         | T <sub>amb</sub> | -40 to 85    | °C   |

#### **Thermal Resistance**

|                  | Parameters | Symbol     | Value | Unit |

|------------------|------------|------------|-------|------|

| Junction ambient | SSO 20     | $R_{thJA}$ | 140   | K/W  |

#### **Electrical Characteristics**

Test conditions (unless otherwise specified);  $V_S = 5$  V,  $T_{amb} = 25$ °C, referred to test circuit System impedance  $Z_O = 50$   $\Omega$ , fiLO = 950 MHz, PiLO = -10 dBm

| Parameters                               | Test Con                                                   | ditions / Pins         | Symbol           | Min. | Тур.            | Max.  | Unit |

|------------------------------------------|------------------------------------------------------------|------------------------|------------------|------|-----------------|-------|------|

| Supply voltage range                     |                                                            | Pins 5 and 6           | $V_{S}$          | 4.75 |                 | 5.25  | V    |

| Supply current                           |                                                            | Pins 5 and 6           | $I_S$            |      | 30              |       | mA   |

| Power down mode, PD                      |                                                            |                        |                  |      |                 |       |      |

| "OFF"mode supply current                 | $V_{PD} \le 0.5 \text{ V}$ $V_{PD} = 1.0 \text{ V}$ Note 1 | Pins 5 and 6<br>Pin 14 | IsPD             |      | ≤ 1<br>20       |       | μΑ   |

| Switch voltage                           |                                                            | Pin 14                 |                  |      |                 |       |      |

| "Power ON"                               |                                                            |                        | VPON             | 4    |                 |       | V    |

| "Power DOWN"                             |                                                            |                        | VPOFF            |      |                 | 1     | V    |

| LO input, LO <sub>in</sub>               | •                                                          | Pin 17                 | •                |      |                 |       |      |

| Frequency range                          |                                                            |                        | fiLO             | 70   |                 | 1000  | MHz  |

| Input level                              | Note 2                                                     |                        | PiLO             | -12  | -10             | -5    | dBm  |

| Input impedance                          | See figure 6                                               |                        | ZiLO             |      | 50              |       | Ω    |

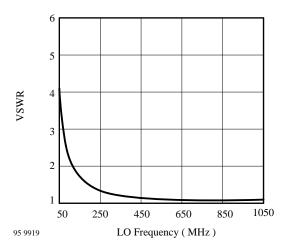

| Voltage standing wave ratio              | See figure 2                                               |                        | VSWRLO           |      | 1.2             | 2     |      |

| Duty cycle range                         |                                                            |                        | LODCR            | 0.4  |                 | 0.6   |      |

| RF input, RF <sub>in</sub>               |                                                            |                        | •                |      |                 |       |      |

| Noise figure (DSB)<br>symmetrical output | @ 950 MHz<br>@ 100 MHz                                     | Note 3<br>Pins 7 and 8 | NF               |      | 12<br>10        |       | dB   |

| Frequency range                          |                                                            | Pins 7 and 8           | fiRF             |      |                 | >fiLO |      |

| -1 dB input compression point            | High gain<br>Low gain                                      | Pins 7 and 8           | ICPHG<br>ICPLG   |      | -8<br>+3.5      |       | dBm  |

| Second order IIP                         | Note 4                                                     | Pins 7 and 8           | IIP2HG           |      | 35              |       | dBm  |

| Third order IIP                          | High gain<br>Low gain                                      | Pins 7 and 8           | IIP3HG<br>IIP3LG |      | +3<br>+13       |       | dBm  |

| LO leakage                               | Symmetric ir<br>Asymmetric                                 |                        | LOL              |      | ≤-60<br>≤-55    |       | dBm  |

| Input impedance                          | see figure 6                                               | Pins 7 and 8           | ZiRF             |      | 500Ω  <br>0.8pF |       |      |

- Note 1: During power down status a load circuitry with dc-isolation to GND is assumed otherwise a current of I  $\approx$  (V<sub>S</sub> -0.8 V)/RI has to be added to the above power down current for each output I, IX, Q, QX.

- Note 2: The required LO-Level is a function of the LO-frequency (see figure 3).

- Note 3: Measured with input matching. For 950 MHz the optional transmission line T3 at the RF input may be used for this purpose. Noise figure measurements without using the differential output signal result in a worse noise figure.

Note 4: Using Pins 7 and 8 as a symmetric RF input, the second order IIP can be improved.

#### **Electrical Characteristics**

Test conditions (unless otherwise specified);  $V_S = 5$  V,  $T_{amb} = 25$ °C, referred to test circuit System impedance  $Z_O = 50 \Omega$ , fiLO = 950 MHz, PiLO = -10 dBm

| Parameters                                               | Test Conditions / Pins                              | Symbol                  | Min. | Тур.        | Max. | Unit            |

|----------------------------------------------------------|-----------------------------------------------------|-------------------------|------|-------------|------|-----------------|

| <b>I/O outputs</b> Emitter follower $I = 0.6 \text{ mA}$ |                                                     | I, IX / Q,<br>QX        |      |             |      |                 |

| 3 dB-bandwidth<br>w/o external C                         | Note 5<br>Pins 1, 2, 19 and 20                      | BWI/Q                   | ≥ 30 |             |      | MHz             |

| I/Q amplitude imbalance                                  | Pins 1, 2, 19 and 20                                | AII/Q                   |      | ≤±0.2       |      | dB              |

| I/Q quadrature error                                     | Pins 1, 2, 19 and 20                                | QEI/Q                   |      | ≤±1.5       |      | Deg             |

| I/Q maximum output swing                                 | Pins 1, 2, 19 and 20 Symm. output $R_L > 5 k\Omega$ | Max I/Q                 |      |             | 2    | V <sub>PP</sub> |

| DC output voltage                                        | Pins 1, 2, 19 and 20                                | VOUT                    |      | 2.8         |      | V               |

| DC output offset voltage                                 | Note 6<br>Pins 1, 2, 19 and 20                      | VOFSI/Q<br>I/IX<br>Q/QX |      | < 5         |      | mV              |

| Output impedance                                         | Pins 1, 2, 19 and 20 see figure 6                   | Zout                    |      | 50          |      | Ω               |

| Gain control, GC                                         |                                                     |                         |      |             | •    |                 |

| Control range power gain, gain high/gain low             | Pin 11<br>Note 7                                    | GCR<br>PGH/GGL          |      | 25<br>23/–2 |      | dB              |

| Switch voltage                                           |                                                     |                         |      |             |      |                 |

| "Gain high"                                              | Pin 11                                              | GCVHigh                 |      |             | 1    | V               |

| "Gain low"                                               | Note 8 Pin 11                                       | GCVLow                  |      |             |      | V               |

| Settling time, ST                                        |                                                     |                         |      |             |      |                 |

| Power "OFF" – "ON"                                       |                                                     | STON                    |      | < 4         |      | μs              |

| Power "ON" – "OFF"                                       |                                                     | STOFF                   |      | < 4         |      | μs              |

- Note 5: Due to test board parasitics this bandwidth is reduced and not equal for I, IX, Q, QX. If symmetry and full bandwidth is required the lowpass Pins 3, 4 and 9, 10 should be isolated from the board. The bandwidth of the I/Q outputs can be increased further by using a resistor between the Pins 3, 4, 9 and 10. This resistors shunt the internal loads of RI  $\sim$  5.4 k $\Omega$  The decrease in gain here has to be considered.

- Note 6: Output emitter follower internal acurrent I=0.6 mA allows only small voltage swing with a 50  $\Omega$  load. For low signal distortion the load impedance should be  $RI \ge 5$  k $\Omega$

- Note 7: Referred to the level of the output vector  $\sqrt{I^2 + Q^2}$ .

- Note 8: The low gain status is achieved with an open or high ohmic Pin 11. A recommended application circuit for switching between high and low gain status is shown in figure 1.

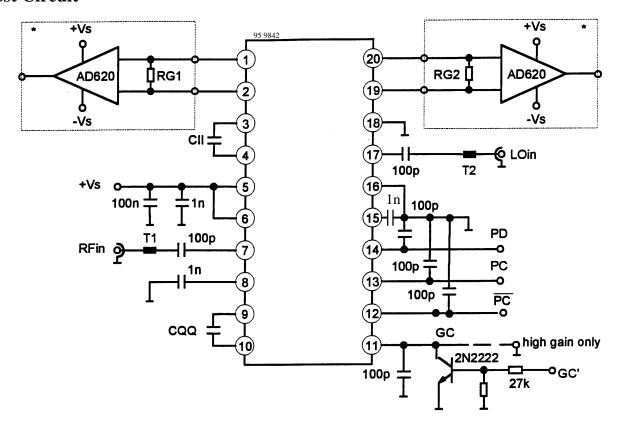

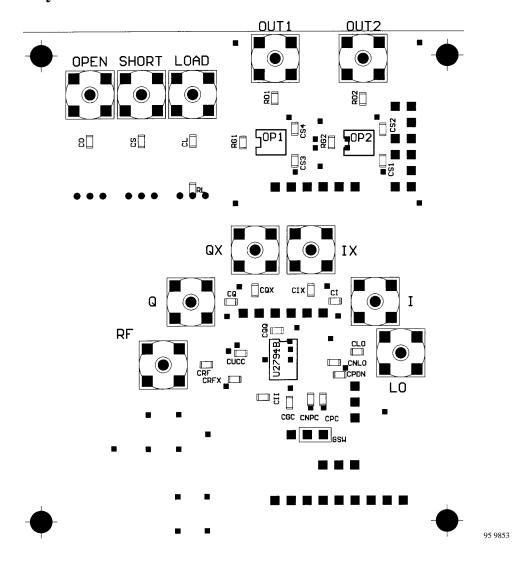

#### **Test Circuit**

<sup>\*</sup> optional for single ended tests (notice 3 dB bandwidth of AD620)

T1, T2 = transmission line  $Z_0 = 50 \Omega$ .

If no GC function is required, connect pin 11 to GND.

For high and low gain status GC' is to be switched to GND respectively to V<sub>S</sub>.

Figure 1.

Rev. A2: 08.06.1995 5 (11)

Figure 2. Typical VSWR frequency response of the LO input

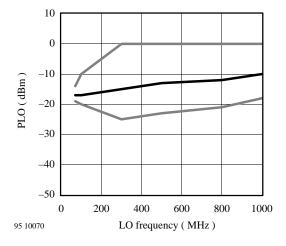

Figure 3. Typical suitable LO power range vs. frequency

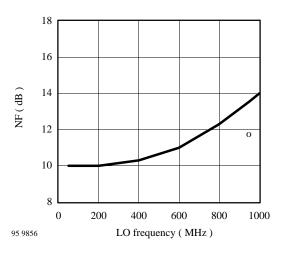

Figure 4. Noise figure vs. LO frequency; o: value at 950 MHz with RF input matching with T3

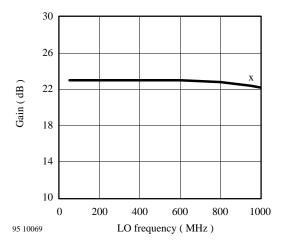

Figure 5. Gain vs. LO frequency; x: value at 950 MHz with RF input matching with T3

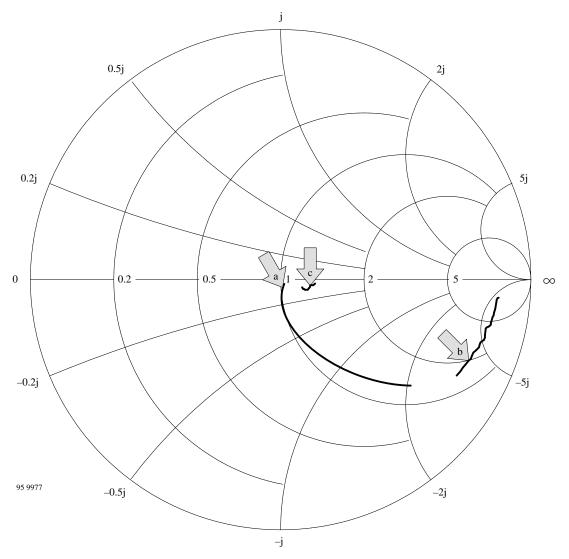

Figure 6. Typical S11 frequency response of the a: LO input, LO frequency from 100 MHz to 1100 MHz, marker: 950 MHz b: RF input, RF frequency from 100 MHz to 1100 MHz, marker: 950 MHz c: I/Q outputs, baseband frequency from 5 MHz to 55 MHz, marker: 25 MHz

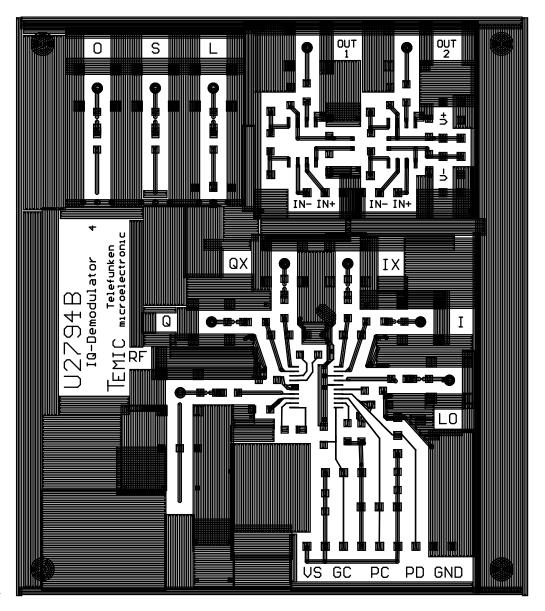

### **Board Layout**

95 9854

#### **Board Layout**

#### **External Components**

CUCC 100 nF CRFX 1 nF CLO 100 pF CNLO 1 nF CRF 100 pF

CII, CQQ optional external lowpass filters

T3 transmission line for RF-input matching,

to connect optionally

CI, CIX, optional for ac-coupling at

CQ, CQX baseband outputs

CPDN 100 pF CGC 100 pF CPC 100 pF CNPC 100 pF GSW gain switch

#### **Calibration Part**

$\begin{array}{cc} \text{CO, CS, CL} & 100 \text{ pF} \\ \text{RL} & 50 \ \Omega \end{array}$

#### **Conversion to Single Ended Output**

OP1, OP2 AD620

RG1, RG2 prog. gain, see datasheet, for  $5.6 \, k\Omega$  a

gain of 1 at 50  $\Omega$  is achieved together

with RD1 and RD2.

RD1, RD2  $450 \Omega$ CS1, CS2 100 nFCS3, CS4, 100 nF

#### **Description of Evaluation Board**

Board material: epoxy;  $\epsilon r = 4.8$ , thickness = 0.5 mm transmission lines:  $Z_O = 50 \Omega$

#### The board offers the following functions

- The test circuit for the U2794B:

- The supply voltage and the control inputs GC, PC and PD are connected via a plug strip. The control input voltages can be generated via external potentiometers; then the inputs should be ac-grounded (time requirements in burst-mode for power up have to be considered).

- The outputs I, IX, Q, QX are dc coupled via an plug strip or can be ac-connected via SMB plugs for high frequency tests e.g. noise figure or s-parameter measurement. The pins II, IIX, QQ, QQX allow user definable filtering with 2 external capacitors CII, CQQ.

- Also the offsets of both channels can be adjusted with two potis or resistors.

- The LO- and the RF-inputs are ac–coupled and connected via SMB plugs. If transmission line T3 is connected to the RF-input and ac-grounded at the other end, gain and noise performance can be improved (input matching to  $50 \Omega$ ).

- The complementary RF-input is ac-coupled to GND (CRFX = 1 nF), the same appears to the complementary LO-input (CNLO = 1 nF).

- A calibration part, which allows to calibrate an s-parameter analyzer directly to the in- and output-signal ports of the U2794B.

- For single-ended measurements at the demodulator outputs, two OP's (e.g., AD620 or other) can be configured with programmable gain; together with an output-divider network RD = 450  $\Omega$  to RL = 50  $\Omega$ , direct measurements with 50  $\Omega$  load-impedances are possible at frequencies < 100 kHz.

#### **Ordering Information**

| Extended Type Number | Package | Remarks |

|----------------------|---------|---------|

| U2794B-FS            | SS0 20  |         |

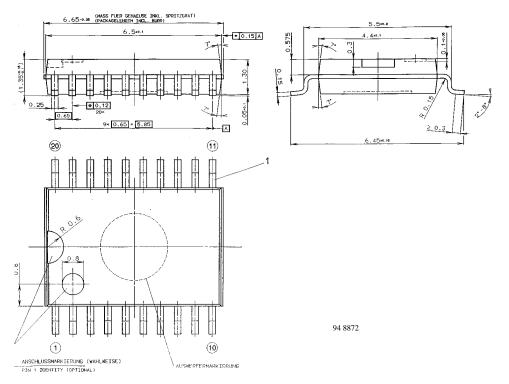

#### **Dimensions in mm**

Package: SSO 20

#### **Ozone Depleting Substances Policy Statement**

It is the policy of TEMIC TELEFUNKEN microelectronic GmbH to

- 1. Meet all present and future national and international statutory requirements.

- 2. Regularly and continuously improve the performance of our products, processes, distribution and operating systems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.

It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).

The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.

**TEMIC TELEFUNKEN microelectronic GmbH** semiconductor division has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.

- 1. Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments respectively

- 2. Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the Environmental Protection Agency (EPA) in the USA

- 3. Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively.

**TEMIC** can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.

We reserve the right to make changes to improve technical design and may do so without further notice.

Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use TEMIC products for any unintended or unauthorized application, the buyer shall indemnify TEMIC against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associated with such unintended or unauthorized use.

TEMIC TELEFUNKEN microelectronic GmbH, P.O.B. 3535, D-74025 Heilbronn, Germany Telephone: 49 (0)7131 67 2831, Fax number: 49 (0)7131 67 2423